評価版をご希望されるお客様は、下記の連絡先へお問い合わせ下さい。

【お問い合わせ先】

株式会社イーエスピー企画

〒501-6257 岐阜県羽島市福寿町平方4-41 岐阜羽島テクノビル

TEL:058-397-0660

FAX:058-397-0661

email:営業/技術 eda@esp.jp

CoDeveloper(Impulse C)

Hardware Generation

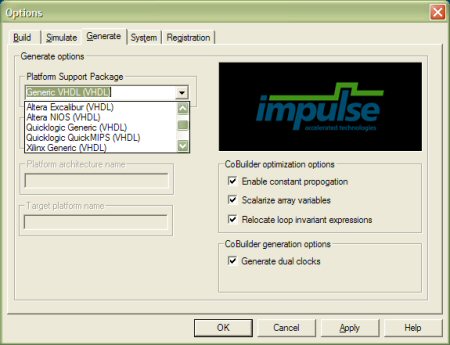

CoMonitorシミュレーションで動作確認され、設計をハードウェア(FPGA)に実装する準備ができたら、ハード化するプロセスを決定しターゲットFPGAを選択します。CoBuilderが動作合成を実行し、対象プロセスはターゲットに最適化されたVHDLコードに変換されます。

■Code generation optionsにより、対象FPGAへのCoBuilder出力の調整 ができます。

CoBuilder は、コンパイルに先立ち、各プロセスを解析して低水準の並行動作を導入できる記述を見つけ、動作をスケジュールしてパイプライン化を試みます。 そして、一般のVHDL論理合成ツールで合成可能のRTL水準のVHDLコードを出力します。出力コードは、選択されたFPGAファミリーに最適化された、ソフトウェア・プロセスとプロセス間通信(ストリーム・バッファ、シグナル、共有メモリ)できるインターフェース・ロジックを含むものです。

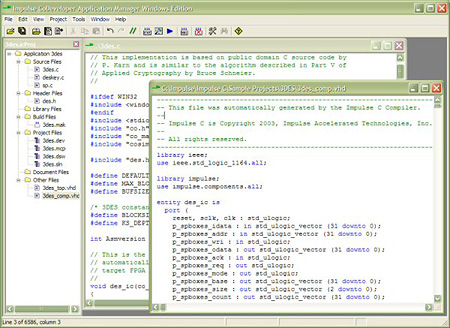

■生成されるVHDLコードは、標準的な論理合成ツールやシミュレータと互換です。

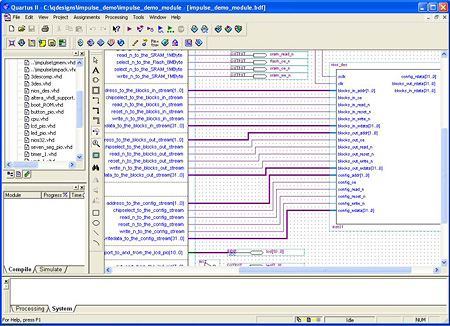

RTL VHDLコードが得られ必要に応じてVHDLシミュレーション(標準的なIEEE準拠VHDLシミュレータかImpulse社のCoValidator)で動作確認をし、 その後のFPGAに実装する過程は、対象FPGAをサポートする標準のFPGAベンダー・ツールで可能です。例えば、Altera社の QuartusⅡにより、CoBuilderにより生成されたVHDLコードは論理合成、最適化、配置配線されAltera Cycloneチップなどに実装できます。以下は、Altera QuartusⅡによる実例です。

■CoDeveloperのインターフェース・ライブラリは、Impulse Cのハードウェア・プロセスとImpulseCのソフトウェア・プロセス(ソフトCPU:Niosなど)を自動接続